## **Signetics**

# TDA8443, TDA8443A RGB/YUV Switch

**Preliminary Specification**

#### Linear Products

#### DESCRIPTION

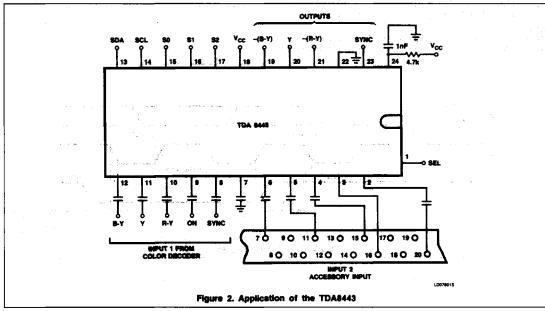

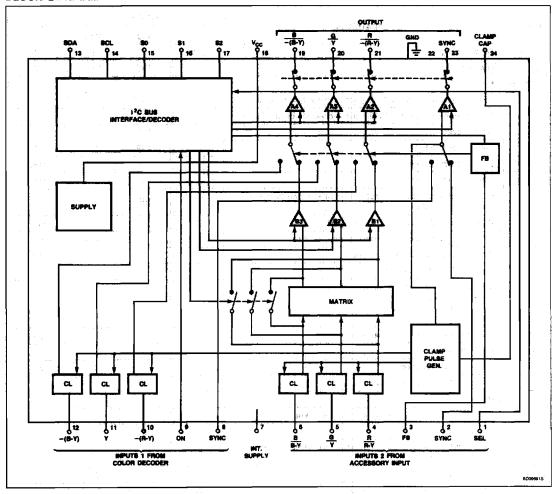

The TDA8443/8443A is intended to be used in color TV sets which have more than one base-band video source. The IC has two sets of inputs. The first (Inputs 1) is intended for the internal video signals (R-Y), Y, (B-Y), and the associated synchronization pulse coming from the color decoder; the second (Inputs 2) is intended for external video signals R, G, B, and the associated synchronization pulse coming from the accessory inputs. The latter ones (inputs 2) can also consist of the video signals (R-Y), Y, (B-Y), and the associated synchronization pulse. The RGB signals at Inputs 2 can also be matrixed internally into the luminance signal Y and the color-difference signals (R-Y) and (B-Y) before they become available at the outputs. By means of I<sup>2</sup>C bus mode or manual control (control by DC voltages), one of these inputs can be selected and will be available at the outputs. The IC contains three pins for programming the sub-address; this means that within one TV set the system can be expanded up to seven ICs. The TDA8443 is designed to be used with the CCTV levels, while the TDA8443A is designed to be used for the standard decoder signal levels.

#### **FEATURES**

- Two RGB/YUV selectable clamped inputs with associated sync

- An RGB/YUV matrix

- 3-State switching with an OFF state

- Four amplifiers with selectable gain

- Fast switching to allow for mixed mode

- I<sup>2</sup>C or non-I<sup>2</sup>C mode (control by DC voltages)

- Slave receiver in the I<sup>2</sup>C mode

- External OFF command

- System expansion possible up to 7 devices

#### **APPLICATIONS**

- TV receivers

- Video switching

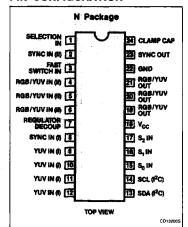

#### PIN CONFIGURATION

#### ORDERING INFORMATION

| DESCRIPTION                  | TEMPERATURE RANGE | ORDER CODE |

|------------------------------|-------------------|------------|

| 24-Pin Plastic DIP (SOT-101) | 0 to +70°C        | TDA8443N   |

| 24-Pin Plastic DIP (SOT-101) | 0 to +70°C        | TDA8443AN  |

#### ABSOLUTE MAXIMUM RATINGS

| SYMBOL                               | PARAMETER                                      | RATING      | UNIT   |

|--------------------------------------|------------------------------------------------|-------------|--------|

| T <sub>STG</sub>                     | Storage temperature range                      | -65 to +150 | °C     |

| TA                                   | Operating ambient temperature range            | 0 to +70    | °C     |

| V <sub>18-7</sub>                    | Supply voltage                                 | 14          | V      |

| Po                                   | Total power dissipation                        |             | w      |

| T <sub>JMAX</sub>                    | Maximum junction temperature                   | 125         | °C     |

| V <sub>SDA</sub><br>V <sub>SCL</sub> | Input voltage range Pin 1:<br>14<br>other pin: | -0.3 to 14  | V<br>V |

| IOMAX                                | Maximum output current                         | TBD         | mA     |

#### **BLOCK DIAGRAM**

## TDA8443, TDA8443A

### DC ELECTRICAL CHARACTERISTICS $T_A = 25$ °C and $V_{CC} = 12V$ , unless otherwise specified.

| 0.//10001               | - A & Commun.                                                                                                   |      |                                       |      |                  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|------|---------------------------------------|------|------------------|

| SYMBOL.                 | PARAMETER                                                                                                       | Min  | Тур                                   | Max  | UNIT             |

| V <sub>18-7</sub>       | Supply voltage                                                                                                  | 10   |                                       | 13.2 | v                |

| I <sub>18</sub>         | Supply current                                                                                                  |      | TBF                                   | TBF  | mA               |

| RGB/YUV                 | channels                                                                                                        |      | · · · · · · · · · · · · · · · · · · · |      |                  |

|                         | Absolute gain difference with respect to programmed value                                                       |      | 0                                     | 10   | %                |

|                         | Relative gain difference between any 2 channels of one input                                                    |      | 0                                     | 5    | %                |

| IN                      | Input current                                                                                                   |      | TBF                                   | 0.3  | μΑ .             |

| Z <sub>OUT</sub>        | Output impedance                                                                                                |      | TBF                                   | - 30 | Ω                |

|                         | 3dB bandwidth (mode 0 or 2)                                                                                     | 1    | 10                                    |      | MHz              |

| :                       | 3dB bandwidth mode 1                                                                                            |      | 10                                    |      | MHz              |

|                         | Mutual time difference at output if all inputs of one source are connected together                             |      | TBF                                   | 25   | ns               |

|                         | Maximum output amplitude of YUV signals                                                                         | 2.8  |                                       |      | V <sub>P-P</sub> |

|                         | Crosstalk between inputs of same source, at 5MHz <sup>1</sup>                                                   |      |                                       | -30  | dB               |

|                         | Crosstalk between different sources                                                                             | T    |                                       | -50  | dB               |

|                         | Isolation (OFF state) at 10MHz                                                                                  | 50   |                                       |      | dB               |

|                         | Differential gain at nominal output signals:<br>R-Y = $1.05V_{P,P}$<br>B-Y = $1.33V_{P,P}$<br>Y = $0.34V_{P,P}$ |      |                                       | 10   | %                |

| S/N                     | Signal-to-noise ratio at nominal input                                                                          | 50   |                                       |      | dB               |

| BW                      | Bandwidth = 5MHz <sup>2</sup>                                                                                   |      |                                       |      |                  |

|                         | Supply voltage rejection <sup>3</sup>                                                                           | 50   |                                       |      | dB               |

|                         | DC level of outputs during clamp                                                                                |      | 5.3                                   |      | ٧                |

| Sync char               | nelš                                                                                                            |      |                                       |      |                  |

|                         | Gain difference with respect to programmed value                                                                | T    |                                       | 10   | %                |

| BW                      | 3dB bandwidth                                                                                                   |      | TBF                                   | ·    | MHz              |

|                         | input amplitude of sync pulse for proper operation of clamp pulse generator                                     | 0.2  | ,                                     | 2.5  | V <sub>P-P</sub> |

| Zout                    | Output impedance                                                                                                |      | TBF                                   | 30   | Ω                |

|                         | Maximum output amplitude (undistorted)                                                                          | 2.5  |                                       |      | Vp.p             |

|                         | DC level on top of sync pulse at output                                                                         | TBF  | 1.8                                   | TBF  | V                |

| I <sup>2</sup> C bus in | puts/outputs                                                                                                    |      |                                       |      |                  |

|                         | SDA input (Pin 13)                                                                                              |      |                                       |      |                  |

|                         | SCL input (Pin 14)                                                                                              |      |                                       |      |                  |

| V <sub>IH</sub>         | Input voltage High                                                                                              | 3    |                                       | Vcc  | V                |

| VIL                     | input voltage Low                                                                                               | -0.3 |                                       | 1.5  | V                |

| l <sub>IH</sub>         | Input current High                                                                                              |      |                                       | 10   | μΑ               |

| I <sub>IL</sub>         | input current Low                                                                                               |      |                                       | 10   | μΑ               |

|                         | SDA output (open-collector)                                                                                     |      |                                       |      |                  |

| V <sub>OL</sub>         | Output voltage Low at IO-L = 3mA                                                                                |      |                                       | 0.4  | ٧                |

| loL                     | Maximum output sink current                                                                                     |      | 5                                     |      | mA               |

## TDA8443, TDA8443A

#### DC ELECTRICAL CHARACTERISTICS (Continued) $T_A = 25^{\circ}C$ and $V_{CC} = 12V$ , unless otherwise specified.

|                  |                                                 |      | eta |                 |      |  |

|------------------|-------------------------------------------------|------|-----------------------------------------|-----------------|------|--|

| SYMBOL           | PARAMETER                                       | Min  | Тур                                     | Max             | UNIT |  |

| Sub-addre        | ss Inputs S0 (Pin 15), S1 (Pin 16), S2 (Pin 17) |      |                                         |                 |      |  |

| VIH              | Input voltage High                              | 3    |                                         | Vcc             | ٧    |  |

| V <sub>IL</sub>  | Input voltage Low                               | -0.3 |                                         | 0.4             | ٧    |  |

| I <sub>IH</sub>  | Input current High                              |      |                                         | TBF             | μΑ   |  |

| I <sub>IL</sub>  | Input current Low                               |      |                                         | TBF             | μА   |  |

| Fast swite       | ching pin                                       |      |                                         |                 |      |  |

| V <sub>3-7</sub> | Input voltage High                              | 1    |                                         | 3               | ٧    |  |

| V <sub>3-7</sub> | Input voltage Low                               | -0.3 |                                         | 0.4             | ٧    |  |

| l <sub>3</sub>   | Input current High                              |      |                                         | TBF             | μА   |  |

| l <sub>3</sub>   | Input current Low                               |      |                                         | TBF             | μΑ   |  |

|                  | Switching delay <sup>4</sup>                    | -    |                                         | TBF             |      |  |

|                  | Switching time <sup>4</sup>                     |      |                                         | TBF             |      |  |

| SEL pin          |                                                 |      |                                         |                 |      |  |

| V <sub>1-7</sub> | Input voltage High                              | 3    |                                         | Vcc             | ٧    |  |

| V <sub>1-7</sub> | Input voltage Low                               | -0.3 |                                         | 0.4             | ٧    |  |

| l <sub>1</sub>   | Input current High                              |      | 4,1                                     | TBF             | μΑ   |  |

| I <sub>1</sub>   | Input current Low                               |      |                                         | TBF             | μΑ   |  |

| ON pin           |                                                 |      |                                         | •               | •    |  |

| V <sub>9-7</sub> | Input voltage High                              | 3    |                                         | V <sub>CC</sub> | ٧    |  |

| V <sub>9-7</sub> | input voltage Low                               | -0.3 |                                         | 1.5             | ٧    |  |

| l <sub>9</sub>   | Input current High                              | 1    |                                         | TBF             | μΑ   |  |

| l <sub>9</sub>   | Input current Low                               |      |                                         | TBF             | μΑ   |  |

#### NOTES:

1. Crosstalk is defined as the ratio between the output signal originating from another input and the nominal output signal on the same output.

2. S/N = 20 $\log \frac{V_{OP-P}}{V_{O} \text{ noise RMS B} = 5\text{MHz}}$

3. Supply voltage rejection = 20tog  $\frac{V_R}{V_R}$  on output

Fast switching input signal

Output signal: YUV

Input : 0V input 1, mode 2

0.75V RGB input 2, mode 1

## TDA8443, TDA8443A

#### **FUNCTIONAL DESCRIPTION**

The circuit contains two sets of inputs: input 1 from the color decoder (color difference signals), and input 2 from the accessory input, RGB, or possibly YUV, both with associated synchronization inputs.

In the RGB mode, the signals are matrixed internally to color difference signals for further processing in a control circuit (e.g., TDA8461).

The inputs are clamped, thus the clamp pulse is internally derived from the sync signals. The outputs can be made high-ohmic (OFF)

in order to be able to put several circuits in parallel.

#### Control

The circuit can be controlled by an I<sup>2</sup>C bus or directly by DC voltages. The fast switching input can be operated by Pin 16 of the accessory input.

#### I2C BUS MODE

The protocol for the TDA8443 for I<sup>2</sup>C bus mode is:

| STA A6 A5 A4 A3 A2 A1 A0 R/W AC D7 D6 D5 D4 D3 D2 D1 D0 /                                     |         |         |         |         |         |          |        |       |      |     |      |       |      |      |    |     |     |       |  |

|-----------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|----------|--------|-------|------|-----|------|-------|------|------|----|-----|-----|-------|--|

| STA   A6   A5   A4   A3   A2   A1   A0   R/W   AC   D7   D6   D5   D4   D3   D2   D1   D0   A |         |         |         |         |         |          |        |       |      |     |      |       |      |      |    |     |     |       |  |

|                                                                                               | C STO   | DO AC   | 2   D1  | ∩3   D2 | Da Da   | ו מסון   | I DA I | דרו ו | I AC | P/W | l ∆∩ | Ι Δ 1 | 1 40 | I AR | 84 | Δ5. | A A | ATS   |  |

| 1 200 1 10 1 10 1 10 1 10 1 10 1 10 1 1                                                       | J 1 0.0 | 20   70 | - 1 - 1 | JU   UE | 54   55 | , 55 , 5 | 00     | ,     | ~~   |     | ~~   | , ,,, | , v. | ~0   |    | 73  | 70  | 1 317 |  |

| STA  | : | Start condition                               | AC : | Acknowledge, generated by the TDA8443 |

|------|---|-----------------------------------------------|------|---------------------------------------|

| A6   | : | 1 }                                           | D7 : | MOD1   mode control bits, see Table 2 |

| A5   | : | 1 fixed address bits                          | D6 : | MODO   mode control bits, see Table 2 |

| A4   | : | 0                                             | D5 : | G2 }                                  |

| АЗ   | : | -1 J                                          | D4 : | G1 gain control bits, see Table 4     |

| A2   | : | Sub-address bit set by S2                     | D3 : | GO J                                  |

| A1   | : | Sub-address bit set by S1                     | D2 : | PRIOR, priority bit                   |

| A0 - | : | Sub-address bit set by S0                     | D1 : | ON/OFF bit                            |

| R/W  | : | Read/Write bit ( = 0 only write mode allowed) | D0 : | ON/OFF active bit                     |

Table 1. Sub-Addressing

| SLA\ | E ADDRESS | BITS       | ADDF | RESS SELECT     | PINS            |

|------|-----------|------------|------|-----------------|-----------------|

| A2   | <b>A1</b> | <b>A</b> 0 | S2   | <b>S</b> 1      | 80              |

| 0    | 0         | 0          | GND  | GND             | GND             |

| 0    | 0         | 1          | GND  | GND             | V <sub>CC</sub> |

| 0    | 1         | 0          | GND  | Vcc             | GND             |

| . 0  | 1         | 1          | GND  | Vcc             | Vcc             |

| 1    | 0         | 0          | Vcc  | GND             | GND             |

| 1    | 0         | 1          | Vcc  | GND             | Vcc             |

| 1    | 1         | 0          | Vcc  | Vcc             | GND             |

| 1    | 1         | 1          | Vcc  | V <sub>CC</sub> | V <sub>CC</sub> |

NOTE:

Non-I<sup>2</sup>C bus operation, see Table 5.

Table 2. Mode Control

| MOD1 | MODO | MODE | FUNCTION                                 |  |  |  |

|------|------|------|------------------------------------------|--|--|--|

| 0    | 0    | 0    | Inputs 2 are selected directly           |  |  |  |

| 0    | 1    | 1    | Inputs 2 are selected via RGB/YUV matrix |  |  |  |

| 1    | 0    | 2    | Inputs 1 are selected directly           |  |  |  |

| 1    | 1    | 3    | Reserved; not to be used                 |  |  |  |

Table 3. Priority Fast Switching Action

| PRIOR | FS     | MODE SELECTED                                                     |

|-------|--------|-------------------------------------------------------------------|

| 0     | ×      | As set by mode control (Table 2)                                  |

| 1     | 0.4V   | Mode 2                                                            |

| 1     | 1 – 3V | Mode 1 if mode 1 is selected<br>Mode 0 if mode 0 or 2 is selected |

## TDA8443, TDA8443A

Table 4. Gain Settings (see Block Diagram)

|    |    |    |                          | TDA8443/C3 |        | TDA8443A/C3 |      |  |

|----|----|----|--------------------------|------------|--------|-------------|------|--|

| G2 | G1 | GO | A1                       | A2, A3, A4 | B1, B3 | B1, B3      | B2   |  |

| 0  | 0  | 0  | 1                        | 1          | -0.6   | -1          | 0.45 |  |

| 0  | 0  | 1  | 1                        | 1          | 1      | 1           | 1    |  |

| 0  | 1  | 0  | Reserved; not to be used |            |        |             |      |  |

| 0  | 1  | 1  | 1                        | 1          | -0.6   | -1          | 0.45 |  |

| 1  | 0  | 0  | 2                        | 2          | -0.6   | -1          | 0.45 |  |

| 1  | 0  | 1  | 2                        | 1          | 1      | 1           | 1    |  |

| 1  | 1  | 0  | 2                        | 2          | 1      | 1           | 1    |  |

| 1  | 1  | 1  | 2                        | 1          | -0.6   | -1          | 0.45 |  |

NOTES:

Matrix equations: relations between output and input signals of the matrix

Y = 0.3R + 0.59V + 0.11B R-Y = 0.7R - 0.59V - 0.11BB-Y = -0.3R - 0.59V + 0.89B

#### ON BIT

| ON | FUNCTION                                  |

|----|-------------------------------------------|

| 0  | OFF, no output signal, outputs high-ohmic |

| 1  | ON, normal functioning                    |

#### OFFACT-ON (Pin 9) Function

| OFFACT | ON | FUNCTIONING                                                            |  |  |  |  |  |

|--------|----|------------------------------------------------------------------------|--|--|--|--|--|

| 0      | L  | OFF                                                                    |  |  |  |  |  |

| 0      | н  | In accordance with last defined D7 - D1 (may be entered while OFF = L) |  |  |  |  |  |

| 1      | X  | In accordance with last defined D7 - D1                                |  |  |  |  |  |

TDA8443, TDA8443A

#### **POWER-ON RESET**

When the circuit is switched on in the I<sup>2</sup>C mode, bits D0 - D7 are set to zero.

**Table 5. Non-I<sup>2</sup>C Bus Mode** (S2 = S1 = S0 = 0)

| CONTROL |     |     | MODE              | GAIN SETTINGS |            |        |          |      |  |  |

|---------|-----|-----|-------------------|---------------|------------|--------|----------|------|--|--|

| SDA     | SCL | SEL | SWITCHED<br>BY FS | TDA8443       |            |        | TDA8443A |      |  |  |

|         |     |     |                   | A1            | A4, A3, A2 | B1, B3 | B1, B3   | B2   |  |  |

| L       | L   | L   | 2/0               | 1             | 1          | 1      | 1        | 1    |  |  |

| L       | L   | н   | 2/0               | 1             | 2          | 1      | 1        | 1    |  |  |

| L       | н   | L   | 2/1               | 1             | 1          | -0.6   | -1       | 0.45 |  |  |

| L       | н   | н   | 2/0               | 1             | 1          | -0.6   | -1       | 0.45 |  |  |

| н       | L.  | L   | 2/0               | 2             | 1          | 1      | 1        | 1    |  |  |

| н       | L   | н   | 2/0               | 2             | 2          | 1      | 1        | 1 .  |  |  |

| Н       | н   | L   | 2/1               | 2             | 1          | -0.6   | -1       | 0.45 |  |  |

| н       | н   | н   | 2/0               | 2             | 1          | -0.6   | -1       | 0.45 |  |  |

#### Fast Switching Input

| FS     | MODE SELECTED                 |  |

|--------|-------------------------------|--|

| ≤ 0.4V | Mode 2                        |  |

| 1 – 3V | Mode 0 or 1 as set by control |  |

#### **ON** Input

| ON | FUNCTION                                  |

|----|-------------------------------------------|

| Ļ  | OFF, no output signal, outputs high-ohmic |

| н  | Functioning as determined in Table 5      |

## TDA8443, TDA8443A

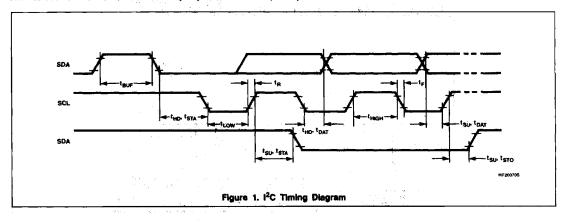

#### 12C BUS LOAD CONDITIONS

$4k\Omega$  pull-up resistor to +5V; 200pF capacitor to GND.

All values are referred to  $V_{IH} = 3V$  and  $V_{IL} = 1.5V$ .

| SYMBOL                             | PARAMETER                             | Min            | Тур | Max | UNIT |  |

|------------------------------------|---------------------------------------|----------------|-----|-----|------|--|

| t <sub>BUF</sub>                   | Bus free before start                 | 4              |     |     | μs   |  |

| tsu, tsta                          | Start condition setup time            | 4              |     |     | μs   |  |

| t <sub>HD</sub> , t <sub>STA</sub> | Start condition hold time             | 4              |     |     | μs   |  |

| t <sub>LOW</sub>                   | SCL, SDA Low period                   | 4              |     |     | μs   |  |

| t <sub>HIGH</sub>                  | SCL High period                       | 4              |     |     | μs   |  |

| t <sub>R</sub>                     | SCL, SDA rise time                    |                |     | 1   | μs   |  |

| t <sub>F</sub>                     | SCL, SDA fall time                    |                |     | 0.3 | μs   |  |

| ISU, IDAT                          | Data setup time (write)               | # A <b>1</b> P |     |     | μs   |  |

| t <sub>HD</sub> , t <sub>DAT</sub> | Data hold time (write)                | 1              |     |     | με   |  |

| tsu, tcac                          | Acknowledge (from TDA8443) setup time |                |     | 2   | μs   |  |

| thd, tcac                          | Acknowledge (from TDA8443) hold time  | 0              |     |     | μs   |  |

#### NOTE:

Timings  $t_{SU},\,t_{DAT}$  and  $t_{HD},\,t_{DAT}$  deviate from the  $l^2C$  bus specification.

After reset has been activated, transmission may only be started after 50 µs delay.

## TDA8443, TDA8443A

Table 6. Application Information

| INPUT 1                       | INPUT 2                                 | OUTPUT                        | MODE | G2 | G1  | GO |

|-------------------------------|-----------------------------------------|-------------------------------|------|----|-----|----|

| YUV/S<br>0.34/~1.33/~1.05/0.3 |                                         | YUV/S<br>0.34/-1.33/-1.05/0.6 | 2    | 1  | 1   | -1 |

| 1 1                           | RGB/S<br>0.75/0.75/0.75/0.3             | many for the second           | 1    | 1  | 1   | 1  |

| YUV/S<br>0.34/-1.33/-1.05/0.3 | * * * * * * * * * * * * * * * * * * * * | YUV/S                         | 2    | 1  | 0   | 0  |

| 0.347 - 1.367 - 1.337 0.3     | RGB/S<br>0.75/0.75/0.75/0.3             | 0.68/-2.66/-2.1/0.6           | 1    | 1. | 0   | 0  |

| YUV/S<br>0.34/-1.33/-1.05/0.3 |                                         | YUV/S<br>0.34/-1.33/-1.05/0.6 | 2    | 1  | 0   | 1  |

|                               | YUV/S<br>0.34/-1,43/-1,05/0.3           |                               | . 0  | 1  | 0   | 1  |

| YUV/S<br>0.34/-1.33/-1.05/0.3 |                                         | YUV/S<br>0.68/-2.66/-2.1/0.6  | 2    | 1  | 1   | 0  |

|                               | YUV/S<br>0.34/-1.33/-1.05/0.3           |                               | 0    | 1  | 1 1 | 0  |