# L4904A

ducital

## DUAL 5V REGULATOR WITH RESET

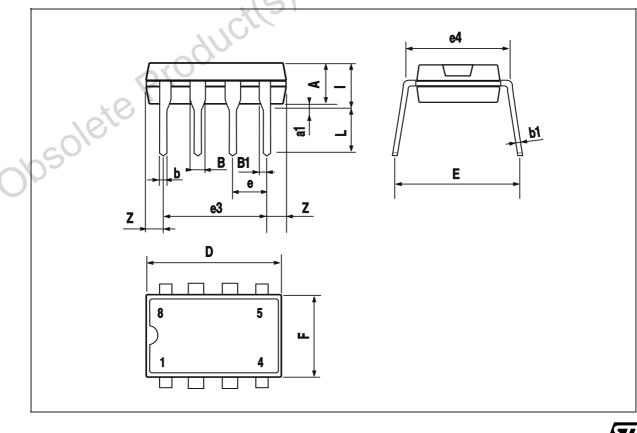

Minidip

ORDERING NUMBER : L4904A

- OUTPUT CURRENTS :  $I_{01} = 50 \text{mA}$  $I_{02} = 100 \text{mA}$

- FIXED PRECISION OUTPUT VOLTAGE 5V ± 2 %

- RESET FUNCTION CONTROLLED BY INPUT VOLTAGE AND OUTPUT 1 VOLTAGE

- RESET FUNCTION EXTERNALLY PRO-GRAMMABLE TIMING

- RESET OUTPUT LEVEL RELATED TO OUTPUT 2

- OUTPUT 2 INTERNALLY SWITCHED WITH ACTIVE DISCHARGING

- LOW LEAKAGE CURRENT, LESS THAN 1μA AT OUTPUT 1

- LOW QUIESCENT CURRENT (Input 1)

- INPUT OVERVOLTAGE PROTECTION UP TO 60V

- RESET OUTPUT NORMALLY HIGH

- OUTPUT TRANSISTORS SOA PROTECTION

- SHORT CIRCUIT AND THERMAL OVER-LOAD PROTECTION

### DESCRIPTION

The L4904A is a monolithic low drop dual 5V regulator designed mainly for subplying microprocessor systems.

Reset and data save functions during switch on/off can be realized.

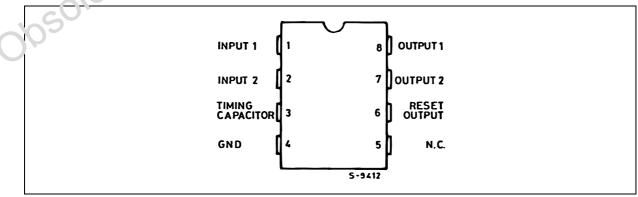

### PIN CONNECTION

### **PIN FUNCTIONS**

| N° | Name                                                                                                                                                                                                           | Function                                                                                                                                                   |  |  |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1  | Input 1                                                                                                                                                                                                        | Low Quiescent Current 50mA Regulator Input.                                                                                                                |  |  |  |  |  |

| 2  | Input 2                                                                                                                                                                                                        | DmA Regulator Input.                                                                                                                                       |  |  |  |  |  |

| 3  | Timing<br>Capacitor                                                                                                                                                                                            | If Reg. 2 is switching-ON the delay capacitor is charged with a $10\mu A$ constant current. When Reg. 2 is switched-OFF the delay capacitor is discharged. |  |  |  |  |  |

| 4  | GND                                                                                                                                                                                                            | Common Ground.                                                                                                                                             |  |  |  |  |  |

| 5  | N.C.                                                                                                                                                                                                           | Not connected.                                                                                                                                             |  |  |  |  |  |

| 6  | $\begin{array}{c c} 6 & Reset \\ Output \end{array} & When pin 3 reaches 5V the reset output is switched high. \\ Therefore t_{RD} = C_t \left(\frac{5V}{10\mu A}\right); t_{RD} (ms) = C_t (nF). \end{array}$ |                                                                                                                                                            |  |  |  |  |  |

| 7  | Output 2                                                                                                                                                                                                       | 5V – 100mA Regulator Output. Enabled if $V_0 1 > V_{RT}$ and $V_{IN 2} > V_{IT}$ . If Reg. 2 is switched-OFF the $C_{o2}$ capacitor is discharged.         |  |  |  |  |  |

| 8  | Output 1                                                                                                                                                                                                       | 5V – 50mA regulator output with low leakage in switch-OFF condition.                                                                                       |  |  |  |  |  |

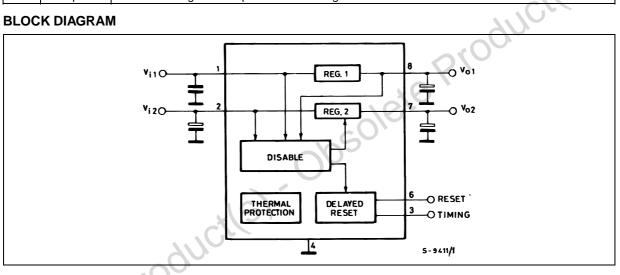

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol          | Parameter                                                  | Value              | Unit   |

|-----------------|------------------------------------------------------------|--------------------|--------|

| V <sub>IN</sub> | DC Input Voltage<br>Transient Input Overvoltage (t = 40ms) | 24<br>60           | V<br>V |

| lo              | Output Current                                             | Internally Limited |        |

| Ptot            | Power Dissipation at $T_{amb} = 50^{\circ}C$               | 1                  | W      |

| Τj              | Storage and Junction Temperature                           | – 40 to 150        | °C     |

### THERMAL DATA

| Symbol                | Parameter                               | Value | Unit |

|-----------------------|-----------------------------------------|-------|------|

| R <sub>th j-amb</sub> | Thermal Resistance Junction-ambient Max | 100   | °C/W |

| Symbol                           | Parameter                          | Test Conditions                                                                                     | Min.                  | Тур.         | Max.                  | Unit   |

|----------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|--------------|-----------------------|--------|

| Vi                               | DC Operating Input Voltage         |                                                                                                     |                       | 0            | 20                    | V      |

| V <sub>01</sub>                  | Output Voltage 1                   | R Load 1kΩ                                                                                          | 4.95                  | 5.05         | 5.15                  | V      |

| V <sub>02 H</sub>                | Output Voltage 2 HIGH              | R Load 1kΩ                                                                                          | V <sub>01</sub> –0.1  | 5            | V <sub>01</sub>       | V      |

| V <sub>02 L</sub>                | Output Voltage 2 LOW               | $I_{02} = -5mA$                                                                                     |                       | 0.1          |                       | V      |

| I <sub>01</sub>                  | Output Current 1                   | $\Delta V_{01} = -100 \text{mV}$                                                                    | 50                    |              |                       | mA     |

| I <sub>L01</sub>                 | Leakage Output 1 Current           | $V_{IN} = 0, V_{01} \le 3V$                                                                         |                       |              | 1                     | μΑ     |

| I <sub>02</sub>                  | Output Current 2                   | $\Delta V_{02} = -100 mV$                                                                           | 100                   |              |                       | mA     |

| V <sub>I01</sub>                 | Output 1 Dropout Voltage (*)       | I <sub>01</sub> = 10mA<br>I <sub>01</sub> = 50mA                                                    |                       | 0.7<br>0.75  | 0.8<br>0.9            | V<br>V |

| VIT                              | Input Threshold Voltage            |                                                                                                     | V <sub>01</sub> + 1.2 | 6.4          | V <sub>01</sub> + 1.7 | V      |

| VITH                             | Input Threshold Voltage Hyst.      | 15)                                                                                                 |                       | 250          |                       | mV     |

| $\Delta V_{01}$                  | Line Regulation                    | $7V < V_{IN} < 18V, I_{01} = 5mA$                                                                   |                       | 5            | 50                    | mV     |

| $\Delta V_{02}$                  | Line Regulation 2                  | 7V < V <sub>IN</sub> < 18V, I <sub>02</sub> = 5mA                                                   |                       | 5            | 50                    | mV     |

| $\Delta V_{01}$                  | Load Regulation 1                  | V <sub>IN</sub> = 8V, 5mA < I <sub>01</sub> < 50mA                                                  |                       | 5            | 20                    | mV     |

| $\Delta V_{02}$                  | Load Regulation 2                  | V <sub>IN</sub> = 8V, 5mA < I <sub>02</sub> < 100mA                                                 |                       | 10           | 50                    | mV     |

| IQ                               | Quiescent Current                  | $I_{02} = I_{01} \le 5mA$<br>$0 < V_{IN} < 13V$<br>$7V < V_{IN} < 13V$                              |                       | 4.5<br>1.6   | 6.5<br>3.5            | mA     |

| lq1                              | Quiescent Current 1                | $\begin{array}{l} 6.3V < V_{IN1} < 13V, \ V_{IN2} = 0 \\ I_{01} \leq 5mA, \ I_{02} = 0 \end{array}$ |                       | 0.6          | 0.9                   | mA     |

| V <sub>RT</sub>                  | Reset Threshold Voltage            |                                                                                                     | V <sub>02</sub> –0.15 | 4.9          | $V_{02} - 0.05$       | V      |

| V <sub>RTH</sub>                 | Reset Threshold Hysteresis         |                                                                                                     | 30                    | 50           | 80                    | mV     |

| V <sub>RH</sub>                  | Reset Output Voltage HIGH          | I <sub>R</sub> = 500μA                                                                              | V <sub>02</sub> – 1   | 4.12         | V <sub>02</sub>       | V      |

| $V_{RL}$                         | Reset Output Voltage LOW           | $I_R = -5mA$                                                                                        |                       | 0.25         | 0.4                   | V      |

| t <sub>RD</sub>                  | Reset Pulse Delay                  | $C_t = 10nF$                                                                                        | 3                     |              | 11                    | ms     |

| t <sub>d</sub>                   | Timing Capacitor Discharge<br>Time | $C_t = 10nF$                                                                                        |                       |              | 20                    | μs     |

| $\frac{\Delta V_{01}}{\Delta T}$ | Thermal Drift                      | $-20^{\circ}C \leq <0>T_{amb} \leq 125^{\circ}C$                                                    |                       | 0.3<br>0.8   |                       | mV/°(  |

| $\frac{\Delta V_{02}}{\Delta T}$ | Thermal Drift                      | − 20°C ≤<0>T <sub>amb</sub> ≤ 125°C                                                                 |                       | 0.3<br>- 0.8 |                       | mV/°(  |

| S <sub>VR1</sub>                 | Supply Voltage Rejection           | $f = 100Hz, V_R = 0.5V, I_o = 50mA$                                                                 | 50                    | 84           |                       | dB     |

| S <sub>VR2</sub>                 | Supply Voltage Rejection           | $f = 100Hz, V_R = 0.5V, I_0 = 100mA$                                                                | 50                    | 80           |                       | dB     |

\* The dropout voltage is defined as the difference between the input and the output voltage when the output voltage is lowered of 25 mV under constant output current condition.

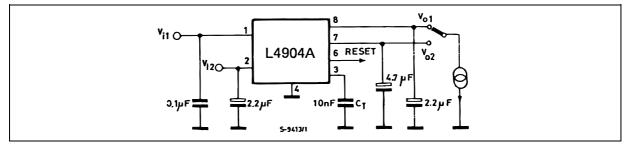

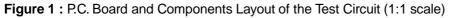

### **TEST CIRCUIT**

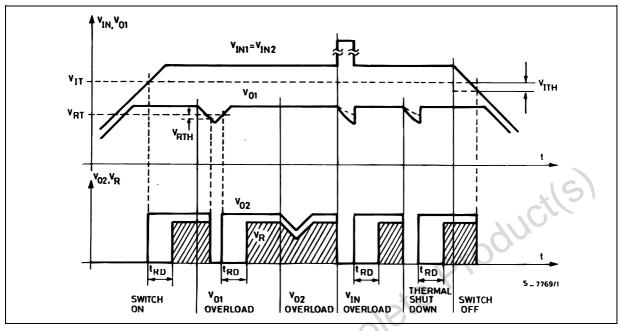

### **APPLICATION INFORMATION**

In power supplies for  $\mu$ P systems it is necessary to provide power continuously to avoid loss of information in memories and in time of day clocks, or to save data when the primary supply is removed. The L4904A makes it very easy to supply such equipments; it provides two voltage regulators (booth 5V high precision) with separate inputs plus a reset output for the data save function.

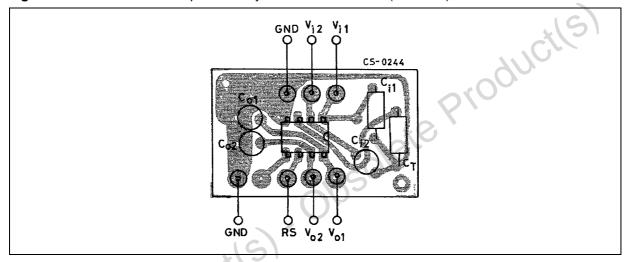

### CIRCUIT OPERATION (see Figure 2)

After switch on Reg. 1 saturates until  $V_{01}$  rises to the nominal value.

When the input 2 reaches  $V_{IT}$  and the output 1 is higher than  $V_{RT}$  the output 2 ( $V_{02}$ ) switches on and the reset output ( $V_R$ ) also goes high after a programmable time  $T_{RD}$  (timing capacitor).

$V_{02} \mbox{ and } V_R$  are switched together at low level when one of the following conditions occurs :

- an input overvoltage

- an overload on the output 1 ( $V_{01} < V_{RT}$ );

- a switch off ( $V_{IN} < V_{IT} - V_{ITH}$ );

and they start again as before when the condition is removed.

An overload on output 2 does not switch Reg. 2, and does not influence Reg. 1.

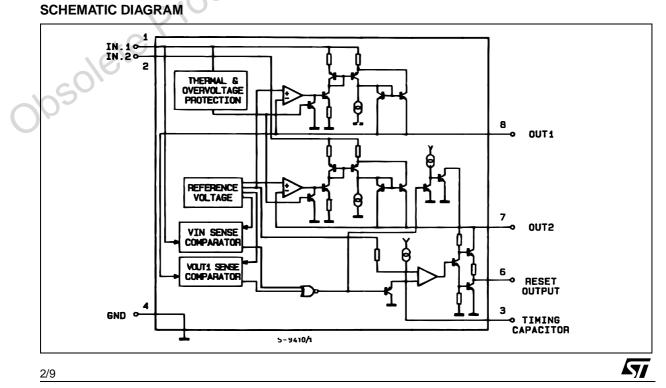

The V<sub>01</sub> output features :

- 5 V internal reference without voltage divider between the output and the error comparator ;

- very low drop series regulator element utilizing mirrors;

permit high output impedance and then very low leakage current even in power down conditions.

This output may therefore be used to supply circuits continuously, such as volatile RAMs, allowing the use of a back-up battery. The  $V_{01}$  regulator also features low consumption (0.6 mA typ.) to minimize battery drain in applications where the  $V_1$  regulator is permanently connected to a battery supply.

The  $V_{02}$  output can supply other non essential 5 V circuits which may be powered down when the system is inactive, or that must be powered down to prevent uncorrect operation for supply voltages below the minimum value.

The reset output can be used as a "POWER DOWN INTERRUPT", permitting RAM access only in correct power conditions, or as a "BACK-UP ENABLE" to transfer data into in a NV SHADOW MEMORY when the supply is interrupted.

### Figure 2

### **APPLICATION SUGGESTIONS**

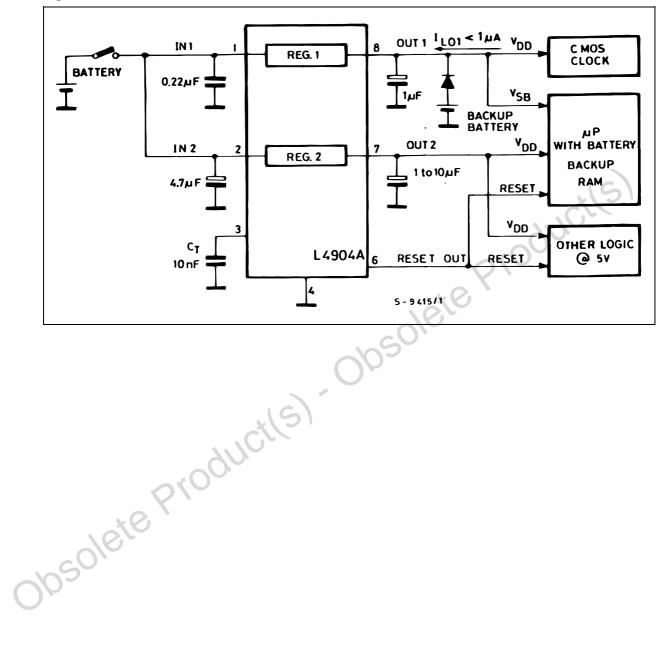

Figure 3 shows an application circuit for a µP system.

Reg. 1 is permanently connected to a battery and supplies a CMOS time-of-day clock and a CMOS microcomputer chip with volatile memory.

Reg. 2 may be switched OFF when the system is inactive.

Figure 4 shows the L4904A with a back up battery on the V<sub>01</sub> output to maintain a CMOS time-of-day

clock and a stand by type C-MOS  $\mu$ P. The reset output makes sure that the RAM is forced into the low consumption stand by state, so the access to memory is inhibit and the back up battery voltage cannot drop so low that memory contents are corrupted.

In this case the main on-off switch disconnects both regulators from the supply battery.

Application Circuits of a Microprocessor system (Figure 3) or with data save battery (Figure 4). The reset output provide delayed rising front at the

### L4904A

### Figure 4

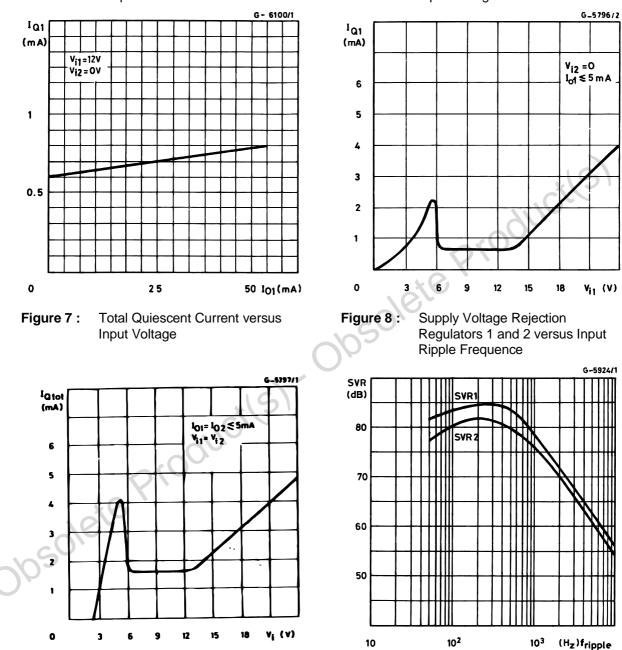

Figure 5 : Quiescent Current (reg. 1) versus Output Current

| L4904A |

|--------|

|--------|

| DIM. | mm    |      |       | inch  |       |       |  |

|------|-------|------|-------|-------|-------|-------|--|

| Dim. | MIN.  | TYP. | MAX.  | MIN.  | TYP.  | MAX.  |  |

| А    |       | 3.32 |       |       | 0.131 |       |  |

| a1   | 0.51  |      |       | 0.020 |       |       |  |

| В    | 1.15  |      | 1.65  | 0.045 |       | 0.065 |  |

| b    | 0.356 |      | 0.55  | 0.014 |       | 0.022 |  |

| b1   | 0.204 |      | 0.304 | 0.008 |       | 0.012 |  |

| D    |       |      | 10.92 |       |       | 0.430 |  |

| Е    | 7.95  |      | 9.75  | 0.313 |       | 0.384 |  |

| е    |       | 2.54 |       |       | 0.100 |       |  |

| e3   |       | 7.62 |       |       | 0.300 |       |  |

| e4   |       | 7.62 |       |       | 0.300 |       |  |

| F    |       |      | 6.6   |       |       | 0.260 |  |

| Ι    |       |      | 5.08  |       |       | 0.200 |  |

| L    | 3.18  |      | 3.81  | 0.125 |       | 0.150 |  |

| Z    |       |      | 1.52  |       |       | 0.060 |  |

57

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

obsolete Product(s)- Obsolete Product(s)

The ST logo is a registered trademark of STMicroelectronics

© 2000 STMicroelectronics - Printed in Italy - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com